Flip-flop (digital elektronik)

En flip-flop er en fællesbetegnelse for en række simple elektroniske kredsløb, opbygget af logiske gates, og som anvendes indenfor den digitale elektronik. Alle flip-flops har to ting til fælles:

- Enhver flip-flop kan antage – og forblive stabil – i én af to forskellige tilstande, svarende til de to digitale signaler "0" og "1". Den ene af to udgange afspejler hvilken tilstand flip-floppen for øjeblikket befinder sig i (kaldes Q), og den anden leverer det komplementære ("modsatte") signal (not-Q).

- En eller flere indgange for styresignaler: Ved at tilføre flip-floppen bestemte digitale signaler gennem disse indgange, kan man få den til at skifte tilstand.

Egenskaben med de to stabile tilstande gør at flip-flops ofte bruges som hukommelse til at opbevare binær information – såkaldt statisk hukommelse (Statisk RAM – 'Random Access Memory') består af et stort antal flip-flops, som hver især husker på én bit information.

Forskellige typer flip-flops

Forskellene mellem de forskellige slags flip-flops ligger i styreindgangen(e), og hvilke signaler der får flip-floppen til at skifte tilstand.

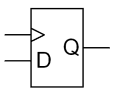

D-flip-flop

En D-flip-flop har en indgang kaldet "D" (Data eller delay – forsinkelse) samt en indgang for et synkroniseringssignal (clock-impuls eller taktgiver-impuls): I det øjeblik synkroniseringssignalet skifter enten fra "0" til "1" eller fra "1" til "0" (ikke ved skift begge veje), registreres signalet på D-indgangen: Er D-signalet "0", antager flip-floppen sin "0"-tilstand; er signalet "1", bringes flip-floppen tilsvarende i "1"-tilstanden. Begge dele uafhængigt af hvilken tilstand flip-floppen stod i før synkroniseringssignalet indløb.

Venstre: Et kredsløbssymbol for en D-type flip-flop, hvor > er clock-impulsen, D er data-input og Q er den gemte data-output.

D flip-flop karakteristiske ligning er:

Sandhedstabellen er:

| D | Q | Qnext |

| 0 | X | 0 |

| 1 | X | 1 |

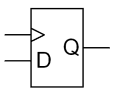

Latch

En latch minder funktionelt lidt om D-flip-floppen, men i modsætning til denne, vil udgangen på en latch (eller transparent latch) afspejle signalet på D-indgangen, ikke blot i det øjeblik synkroniseringssignalet (clock-input) skifter, men i hele det tidsrum hvor synkroniseringssignalet er høj. Når clock-input skifter fra høj-til-lav bliver D-input værdien i samme øjeblik gemt og denne værdi er nu Q-output, indtil clock-input går høj igen. I den analoge verden svarer en latch til et sample-and-hold kredsløb.

J/K-flip-flop

Den såkaldte J/K-flip-flop har en indgang for synkroniseringssignaler samt to indgange for styresignaler, kaldet "J" og "K". Når styresignalet skifter skifter enten fra "0" til "1" eller fra "1" til "0" (ikke ved begge slags skift), gør den én af fire ting:

- Hvis både J- og K-indgangen begge er "0", sker der ingenting – J/K-flip-floppen bibeholder sin hidtidige tilstand.

- Hvis J er "0" og K er "1", skifter flip-floppen til "0"-tilstanden, uanset hvilken tilstand den var i før.

- Hvis J er "1" og K er "0", skifter flip-floppen til "1", uanset tilstanden indtil skiftet.

- Hvis både J og K er "1", skifter flip-floppen tilstand: Var den i "0"-tilstand, skifter den til "1"; var den oprindeligt i "1"-tilstanden, skifter den til "0".

Venstre: Kredsløbssymbolet for en J-K flip-flop, hvor > er clock-input, J og K er data-input, Q er det gemte data-output, og Q' er den inverse Q.

Den karakteristiske ligning for en J-K flip-flop er:

og sandhedstabellen er:

| J | K | Q | Qnext |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | X | 0 |

| 1 | 0 | X | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

J-K flip-flop er opkaldt efter Jack Kilby, som opfandt det integrerede kredsløb i 1958, for hvilket han fik Nobelprisen for i fysik i 2000. "Jump-kill", er en analogi til "set-reset", som er et backronym.

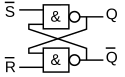

R/S-flip-flop

RS-flip-floppen har mindst to indgange, kaldet henholdsvis "R" og "S" (fra de engelske ord "reset" og "set"): Når "S"-indgangen aktiveres, bringes flip-floppen over i "1"-tilstanden. Hvis flip-floppen i forvejen var i "1"-tilstanden, sker der ikke noget. Tilsvarende vil en aktivering af "R"-indgangen bringe flip-floppen i "0"-tilstanden, uanset hvilken tilstand den var i tidligere.

RS-flip-floppen findes i to varianter; en uden clock-input og en med clock-input.

Den uden clock-input trigger på høj-til-lav-flanker (nand-gate baseret) eller lav-til-høj-flanker (nor-gate baseret) for S og R. Sandhedstabellens S og R 0 og 1 skal så fortolkes som flankeskift.

Den med clock-input trigger på clock-input høj-til-lav-flanker og Q bestemmes i dette øjeblik så af S og R værdierne.

Sandhedstabellen for en SR flip-flop er:

| S | R | Qnext |

| 0 | 0 | hold |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | ustabil |

mere eksplicit kan før-clock værdien af Q indgå som et retmæssigt input:

| S | R | Q | Qnext |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | X | 0 |

| 1 | 0 | X | 1 |

| 1 | 1 | X | ustabil |

X betyder "underordnet" eller at output vil være det samme lige meget hvilken tilstand X er i.

Venstre: Kredsløbssymbolet for en SR-type flip-flop, hvor > er clock-input, S er set-input, R er reset-input, Q er den gemte data-output, og Q' er den inverse af Q.

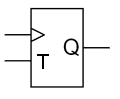

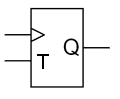

T-flip-flop

En T-flip-flop har en enkelt indgang, benævnt "T": Når signalet på denne indgang skifter enten fra "0" til "1" eller fra "1" til "0" (ikke ved begge slags skift), skifter flip-floppen tilstand: Var den i "0"-tilstand før det relevante skift indtraf på T-indgangen, skifter den til "1"; var den oprindeligt i "1"-tilstanden, skifter den til "0".

Dens opførsel kan beskrives ved følgende karakteristiske ligning:

og sandhedstabellen er:

| T | Q | Qnext |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Venstre: Kredsløbssymbolet for en T-type flip-flop, hvor > er clock-input, T er toggle-input og Q er den gemte data-output.

Kilder/referencer

- Radio electronics: R S-Flip Flop Circuit – two logic or digital circuits for an R S flip flop, one using NAND gates and the other using NOR gates Arkiveret 29. oktober 2005 hos Wayback Machine Citat: "...useful application for a simple R S flip flop is as a switch de-bounce circuit..."

- play-hookey.com: The D Latch Arkiveret 9. september 2005 hos Wayback Machine

Se også

Eksterne henvisninger

| Wikimedia Commons har medier relateret til: |

Medier brugt på denne side

RS Flipflop constructed in NAND tech with Clock

Forfatter/Opretter: MichaelFrey 2006-08-29 17:01 (UTC), Licens: CC BY-SA 2.0 de

Flip-flops

Forfatter/Opretter: DrJolo, Licens: CC BY-SA 3.0

Basic animated interactive BJT bistable multivibrator circuit.

A JK flip flop